УДК 681.391

### МЕТОДЫ И АППАРАТУРА КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ НИЗКОПЛОТНОСТНЫХ КВАЗИЦИКЛИЧЕСКИХ КОДОВ

Кравченко А.Н., к.т.н., проектировщик систем Ubiso GmbH, Germany, e-mail: alexander.kravtchenko@ubiso.com

**Ключевые слова:** кодирование, декодирование, низкоплотностное, LDPC коды, проверочная матрица, кодовая скорость.

#### Введение

Системы связи и вещания, в частности беспроводные системы, часто подвержены помехам, в связи с чем использование помехоустойчивых кодов имеет важное значение. Среди помехоустойчивых кодов LDPC коды, предложенные Галлагером [1] и позже вновь открытые Маккеем и Нилом [2], появляются

как класс кодов, которые обладают эффективной способностью исправлять ошибки в каналах связи. Превосходная эффективность декодирования этих кодов получается при использовании алгоритма декодирования, вычисляющего итеративно распределение вероятностей в граф-орентированной модели, который известен в литературе как «belief propagation algorithm» (BPA). В отечественной литературе этот метод известен как алгоритм декодирования с итеративным распространением доверия (АРД) [3]. Следует отметить, что в литературе существует большое количество модификаций этого алгоритма (алгоритмы, основывающиеся на логарифмическом отношении функций правдоподобия, упрощенные методы). Некоторые сведения о модификациях можно найти в [11]. В настоящее время LDPC коды со средней пропускной способностью используются в стандартах как DVB-S2, WiMax(IEEE 802.16e) и WLAN(IEEE 802.11n). Более того, LDPC коды с высокой пропускной способностью используются в стандарте WPAN (IEEE 802.15.3c). Следует отметить, что во всех перечисленных стандартах используются квази-циклические низкоплотностные коды (QC-LDPC).

### QC-LDPC коды, основные определения

LDPC коды универсально специфицируются их проверочными матрицами. Проверочная матрица QC-LDPC кода задается как массив циркулянтов (перестановочных матриц) одного и того же размера. Циркулянт [4] представляет собой квадратную матрицу  $(b \times b)$ , в которой каждая последующая строка является циклическим сдвигом вправо на одно место предыдущей строки. Индекс сдвига определяет позицию «1» в первой строке матрицы. Весы строк и столбцов в циркулянте одни и те же, скажем к примеру w=1. Для простоты можно сказать, что циркулянт имеет вес Хэмминга w. Если w=1, то циркулянт есть циклическая перестановочная матрица. Циркулянт полностью характеризуется его первой стро-

Произведен анализ проверочных матриц нерегулярных квазициклических низко-плотностных кодов WPAN (IEEE 802.15.3c) стандарта (QC-LDPC). Установлено, что проверочные матрицы являются квадратичными и обратимыми. В связи с этим к расчету порождающих матриц применен традиционный метод с приложением к квазициклическим низкоплотностным кодам. Приведены методы кодирования и декодирания QC-LDPC кодов на основе проверочных матриц. Предложена аппаратура кодирования этих кодов. Представлены результаты моделирования эффективности декодирования LDPC кодов WPAN-стандарта в канале с АБГШ для случая двоичной фазовой модуляции.

кой (или первым столбцом), которую называют генератором циркулянта. LDPC код определяется матрицей размера  $n \times m$ , где n длина кода и m число проверочных бит в коде. Число имформационых бит определяется как k=n-m. Проверочная матрица  $\mathbf{H}_{\rm qc}$  QC-LDPC кода с размерностью  $t \times c$ , где  $n=b \times t$  и  $m=b \times c$ , может быть построена путем соединения  $t \times c$  циклических перестановочных матриц размерности  $(b \times b)$ .

Матрица  $\mathbf{H}_{_{qc}}$  QC-LDPC кода для двух натуральных чисел t и c с  $c \le t$  может быть определена как массив циркулянтов  $\mathbf{A}_{::}$  в поле GF(2):

$$\mathbf{H}_{qc} = \begin{bmatrix} \mathbf{A}_{1,1} & \mathbf{A}_{1,2} & \cdots & \mathbf{A}_{1,t} \\ \mathbf{A}_{2,1} & \mathbf{A}_{2,2} & \cdots & \mathbf{A}_{2,t} \\ \vdots & \vdots & \ddots & \vdots \\ \mathbf{A}_{c,1} & \mathbf{A}_{c,2} & \cdots & \mathbf{A}_{c,t} \end{bmatrix}$$

(1)

Структуру QC-LDPC кода можно определить на основе его проверочной матрицы в циркулянтной форме, определенной формулой (1). На основе этой формы, каждая кодовое слово  ${\bf v}$  может быть разделено на секции  ${\bf v}=(v_1,v_2,\cdots,v_i)$ , и каждая секция  $v_j$  включает b компонент (бит). Для  $1\leq j\leq t$ , b компонент j-ой секции соответствуют b столбам j-го столбца циркулянта в  ${\bf H}_{\rm cc}$ .

### Анализ проверочных матриц и метод кодирования

LDPC коды, используемые в системе WPAN [5], являются систематическими нерегулярными QC-LDPC кодами. Табл. 1 для примера иллюстрирует проверочную матрицу LDPC кода с кодовой скоростью R = 7/8.

Индекс -1 определяет нулевую перестановочную матрицу (матрица состоит из одних нулей). Проверочная матрица состоит из двух частей  $\mathbf{H}_{\rm qc} = [\mathbf{H}_1 \ \mathbf{H}_2]$ , где  $\mathbf{H}_1$  субматрица соответствует информационным битам, и  $\mathbf{H}_2$  представляет проверочные биты кодового слова. Кодовое слово должно удовлетворять уравнению  $\mathbf{H}_{\infty} \cdot \mathbf{v}^{\rm T} = 0$ .

| Таблица 1. Проверочная матри⊔ | а LDPC кода с кодовой скоростью R = 7/8 |

|-------------------------------|-----------------------------------------|

|                               |                                         |

| 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0  | 18 | 6  | 5  | 7  | 18 | 16 | 0  | 10 | 2  | 3  | 6  | 10 | 16 | 9  | 0  | 20 | 7  | 9  | 5  | 4  | 12 | 4  | 4  | 4  | 10 | 19 | 5  | 10 | -1 | -1 | -1 |

| 5  | 0  | 18 | 6  | 0  | 7  | 18 | 16 | 6  | 10 | 2  | 3  | 0  | 10 | 16 | 9  | 5  | 20 | 7  | 9  | 4  | 4  | 12 | 4  | 5  | 4  | 10 | 19 | 19 | 10 | -1 | -1 |

| 6  | 5  | 0  | 18 | 16 | 0  | 7  | 18 | 3  | 6  | 10 | 2  | 9  | 0  | 10 | 16 | 9  | 5  | 20 | 7  | 4  | 4  | 4  | 12 | 19 | 5  | 4  | 10 | 17 | 19 | 10 | -1 |

| 18 | 6  | 5  | 0  | 18 | 16 | 0  | 7  | 2  | 3  | 6  | 10 | 16 | 9  | 0  | 10 | 7  | 9  | 5  | 20 | 12 | 4  | 4  | 4  | 10 | 19 | 5  | 4  | 7  | 17 | 19 | 10 |

Анализ проверочных матриц всех кодов показывает, что  $\mathbf{H}_2$  - части матриц  $\mathbf{H}_{qc}$  квадратичны и обратимы, в том числе и для LDPC кода с R=7/8. В этом случае для расчета порождающей матрицы  $\mathbf{G}_{qc}$  может быть использован традиционный метод [6] с применением к QC-LDPC кодам. Исходя из этого, субматрицу  $\mathbf{H}_2$  можно представить в виде

$$\mathbf{H}_{2} = \begin{bmatrix} \mathbf{A}_{1,t-c+1} & \mathbf{A}_{1,t-c+2} & \cdots & \mathbf{A}_{1,t} \\ \mathbf{A}_{2,t-c+1} & \mathbf{A}_{2,t-c+2} & \cdots & \mathbf{A}_{2,t} \\ \vdots & \vdots & \ddots & \vdots \\ \mathbf{A}_{c,t-c+1} & \mathbf{A}_{c,t-c+2} & \cdots & \mathbf{A}_{c,t} \end{bmatrix}$$

(2)

Порождающая матрица может быть представлена как

$$\begin{aligned} \mathbf{G}_{\text{qc}} = & \begin{bmatrix} \mathbf{G}_{1} \\ \mathbf{G}_{2} \\ \vdots \\ \mathbf{G}_{t-c} \end{bmatrix} = \begin{bmatrix} \mathbf{I} & \mathbf{O} & \cdots & \mathbf{O} & \mathbf{G}_{1,1} & \mathbf{G}_{1,2} & \cdots & \mathbf{G}_{1,c} \\ \vdots & \mathbf{I} & \cdots & \mathbf{O} & \mathbf{G}_{2,1} & \mathbf{G}_{2,2} & \cdots & \mathbf{G}_{2,c} \\ \vdots & \vdots & \ddots & \vdots & \vdots & \vdots & \ddots & \vdots \\ \mathbf{O} & \mathbf{O} & \cdots & \mathbf{I} & \mathbf{G}_{t-c,1} & \mathbf{G}_{t-c,2} & \cdots & \mathbf{G}_{t-c,c} \end{bmatrix} = \\ = & \begin{bmatrix} \mathbf{I}_{(t-c)b} & \mathbf{P} \end{bmatrix}, \end{aligned}$$

(3)

где  ${f I}$  - единичная матрица размерности  $b \times b$  ,  ${f O}$  - нулевая матрица размерности  $b \times b$  и  ${f G}_{{\bf i},{\bf j}}$  - циркулянты с  $1 \le i \le t-c$  и  $1 \le j \le c$  и размерностью  $b \times b$  .

Порождающая матрица (3) состоит из двух частей: левой части  $\mathbf{I}_{(\mathbf{t}-\mathbf{c})b}$  и правой части  $\mathbf{P}$ . Левая часть матрицы  $\mathbf{I}_{(\mathbf{t}-\mathbf{c})b}$ с  $(t-c)b\times(t-c)b$  представляет собой единичные матрицы, расположенные на главной диагонали, а правая часть - массив циркулянтов. Представление кода в форме (3) является систематическим представлением [6]. Левая часть отображает информационные биты кодового слова, правая часть - его проверочные биты. Необходимым и достаточным условием для существования порождающей матрицы  $\mathbf{G}_{qc}$  является условие  $\mathbf{H}_{qc}\mathbf{G}_{qc}^{\mathrm{T}} = \mathbf{O}$ . Допустим  $\mathbf{g}_{i,j}$  представляет собой генератор циркулянта  $\mathbf{G}_{i,j}$ . Когда  $\mathbf{g}_{i,j}$  известны, можно сформировать все циркуланты порождающей матрицы  $\mathbf{G}_{qc}$ .

Таким образом  $\mathbf{G}_{qc}$  характерезируется полностью группой c(t-c) генераторов. Допустим  $\mathbf{u}=(1,0,\cdots,0)$  есть группа из b бит с '1' в первой позициии и  $\mathbf{0}=(0,0,\cdots,0)$  - группа, которая содержит только нули. Для  $1\leq i\leq t-c$  первый ряд субматрицы  $\mathbf{G}_{i}$  определяется следующим образом

$$g_{i} = (0 \cdots 0 u 0 \cdots 0 g_{i,1} g_{i,2} \cdots g_{i,c}),$$

(4)

где группа  ${\bf u}$  находится в i - ой позиции  ${\bf g}_i$  .

Обозначим  $z_i = (\mathbf{g}_{i,1} \ \mathbf{g}_{i,2} \cdots \mathbf{g}_{i,c})$  и  $\mathbf{H}_1^{(i)} = \left[\mathbf{A}_{1,i}^{\mathrm{T}} \cdots \mathbf{A}_{c,i}^{\mathrm{T}}\right]^{\mathrm{T}}$ . Тогда выражение  $\mathbf{H}_{\mathrm{qc}} \mathbf{g}_i^{\mathrm{T}} = \mathbf{0}$  дает следующее равенство:

$$\mathbf{H}_{1}^{(i)}\mathbf{u}^{\mathrm{T}} + \mathbf{H}_{2}\mathbf{z}_{i}^{\mathrm{T}} = \mathbf{0} . \tag{5}$$

Поскольку  ${\bf H}_2$  есть квадратная матрица и имеет полный ранг, то она обратима. Тогда из (5) следует

$$\mathbf{z}_{i}^{T} = \mathbf{H}_{2}^{-1} \mathbf{H}_{1}^{(i)} \mathbf{u}^{T} . \tag{6}$$

Решение (6) для  $1 \leq i \leq t-c$  дает все генераторы  $\mathbf{g}_{i,j}$  порождающей матрицы  $\mathbf{G}_{qc}$  .

Обозначим  $\mathbf{a}=(a_1,a_2,\cdots,a_{(t-c)b})$  как информационную последовательность бит (t-c)b, подлежащих кодированию. После деления информационых бит на секции (t-c) равной длины  $\mathbf{a}=(\mathbf{a_1},\mathbf{a_2},\cdots,\mathbf{a_{t-c}})$ , кодовое слово можно представить в форме  $\mathbf{v}=\mathbf{aG_{qc}}$ , которое имеет систематическое представление:  $\mathbf{v}=(\mathbf{a},\mathbf{p_1},\mathbf{p_2},\cdots,\mathbf{p_c})$ . Здесь  $\mathbf{p_1},\mathbf{p_2},\cdots,\mathbf{p_c}$  - секции равной длины b, где каждая секция представляет собой проверочные биты  $\mathbf{p_j}=(p_{j,1},p_{j,2},\cdots,p_{j,b})$ . Проверочные биты в каждой секции вычисляются в соответствии с выражнием

$$\mathbf{p}_{i} = \mathbf{a}_{1} \mathbf{G}_{1,i} + \mathbf{a}_{2} \mathbf{G}_{2,i} + \cdots + \mathbf{a}_{t-c} \mathbf{G}_{t-c,i}. \tag{7}$$

На основании рассмотренного метода были вычислены генераторы для всех порождающих матриц стандарта. Например, рис. 1 иллюстрирует генераторы, вычисленные для LDPC кода с кодовой скоростью R=7/8.

Рис. 1. Генераторы порождающей матрицы для LDPC кода с R=7/8

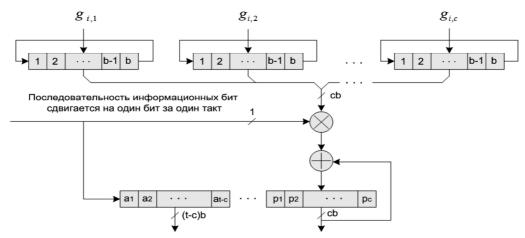

Рис. 2. Структура кодера

Представление  $\mathbf{G}_{qc}$  в виде генераторов очень практично при разработке аппаратуры. В основе кодера лежит циклический сдвигающий регистр, который первоначально загружается генератором и в процессе последовательных сдвигов реализует циркулянт. Рис. 2 представляет структуру кодера. Кодер передает информационные биты на выход, как биты кодового слова. Одновременно кодер вычисляет проверочные биты  $\mathbf{p}_{\mathbf{j}}=(p_{\mathbf{j},\mathbf{l}},p_{\mathbf{j},\mathbf{2}},\cdots,p_{\mathbf{j},b})$  путем последовательного выполнения умножения циркулянтов на группы информационных бит. Непосредственное осуществление матричного умножения показано на рис. 2, как это предлагает Лин [7].

Циклические сдвигающие регистры, каждый длины b, загружаются генераторами (первая строка рис. 1). Для каждого информационного бита  $a_m$  ( $m=1,\cdots,(t-c)b$ ) , в свою очередь, эти регистры циклически сдвигаются один раз. Если  $a_m=1$ , то выполняется операция ХОR и результат загружается в выходной регистр (проверочные биты). Когда операция перемножения циркулянтов на информационные биты группы завершена, следующие генераторы  $g_{1,1}, g_{1,2}, \cdots, g_{1,c}$  загружаются в регистры сдвига, и операция кодирования повторяется. Процесс кодирования завершается, когда последняя группа циркулянтов (27, рис. 1) перемножается на последнюю группу информационых бит (27). После кодирования все проверочные биты находятся в выходном регистре.

# Декодирование QC-LDPC кодов

Для декодирования QC-LDPC кодов широко используется алгоритм послойного декодирования (layered decoding), развитый в работах [8-9]. Применение этого алгоритма для декодирования кодов в стандартах DVB-S2, WiMax(IEEE 802.16e) и WLAN(IEEE 802.11n) изложено в работе [10]. В настоящей работе этот алгоритм применен для декодирования кодов стандарта WPAN (IEEE 802.15.3c). Коротко остановимся на особенностях алгоритма:

- 1. Декодер, спроектированный при использовании этого алгоритма, требует меньшего объема памяти чем стандартый декодер, реализирующий стандартный двухфазный метод декодирования — «сумма произведение» (two-phase message-passing, TPMP algorithm) [10].

- 2. Скорость сходимости алгоритма существенно выше чем у «ТРМР» (алгоритм выполняет меньше итераций

для достижения равной эффективности декодирования).

При описании алгоритма воспользуемся метрикой, называемой логарифмическим отношением функций правдоподобия (log-likelihood ratio - LLR), которая определяется выражением

$$LLR(x \mid y) = \ln \left[ \frac{p(y \mid x = 0)}{p(y \mid x = 1)} \right].$$

Допустим,  $x=[x_1,x_2,\ldots,x_n]$  обозначает кодовое слово, которое модулируется при использовании двоичной фазовой модуляции, и модулированные значения х передаются по каналу с белым аддитивным гауссовым шумом (АБГШ). Допустим  $y=[y_1,y_2,\ldots,y_n]$  обозначает входную последовательность принятых сигналов (символов). Демодулятор принимает входную последовательность сигналов и вычисляет соответствующие LLR значения для:  $j=1,2,\ldots,n$

$$\lambda_{j} = LLR(y_{j} | x_{j}) = \ln \left[ \frac{p(y_{j} | x_{j} = 0)}{p(y_{j} | x_{j} = 1)} \right].$$

(8)

Обычно при двоичной биполярной передаче по каналу LLR значения вычисляются как

$$\lambda_{j} = \frac{2}{\sigma^{2}} * y_{j} \tag{9}$$

где  $\sigma^2$  - дисперсия АБГШ.

При описании алгоритма воспользуемся следующими обозначениями:

$\lambda_{_j}$  - «LLR» значение принятого j-го символа,  $R_{_{ij}}[k]$  – внешние (extrinsic) «LLR» значения,  $Q_{_{ij}}[k]$  – внутренние (intrinsic) «LLR» значения,  $\Lambda_{_j}$  - апостериорные «LLR» значения

Выполнение алгоритма осуществляется в следующем порядке:

1. Инициализация:

$$R_{ii}^0 = 0, \Lambda_i^0 = \lambda_i. \tag{10}$$

2. Горизонтальное сканирование (check node update rule):

$$Q_{ii}^{(k)} = \Lambda_{i}^{(k-1)} - R_{ii}^{(k-1)};$$

(11)

$$R_{ij}^{(k)} = \prod_{j \in R\{i\} \setminus j} sign(Q_{ji}^{(k)}) * \{MIN_{j \in R\{i\} \setminus j} \mid Q_{ji}^{(k)} \mid \};$$

(12)

$$\Lambda_{i}^{(k)} = Q_{ii}^{(k)} + R_{ii}^{(k)}, \tag{13}$$

где k – текущая итерация.

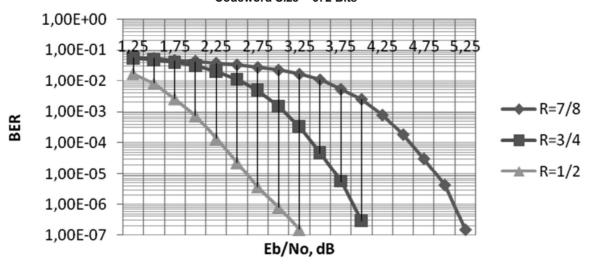

### Codeword Size = 672 Bits

Рис. 3. Еффективность декодера для кодовых скоростей – 1/2, 3/4, 7/8

Твердое решение декодера (hard decision) после каждой итерации осуществляется на основе проверки условия -  $\nu=1$  , если  $\Lambda^{(k)}_{-} \leq 0$  , иначе  $\nu=0$  .

Шаг 2 выполняется до тех пор, пока не выполнится условие -  $\mathbf{H}_{_{\mathrm{qc}}} \cdot \mathbf{v}^{\mathrm{T}} = 0$  или будет достигнуто максимальное значение итераций. При вычислении  $R_{_{||}}[k]$  используется метод, основанный на минималиной сумме (Min-sum - аппроксимация) [11]. Данный алгоритм хорошо реализируется в аппаратуре декодера [12]. На рис. 3 представлены резултаты моделирования эффективности декодирования LDPC кодов WPAN-стандарта в канале с АБГШ для случая двоичной фазовой модуляции.

При моделировании декодера использовалась арифметика с фиксированной запятой. Для представления мягких решений (LLR значений) демодулятора и сообщений внутри декодера использовался прямой код с числом разрядов b = 8.

#### Литература

- 1. R. G. Gallager, Low-Density Parity-Check Codes, MIT Press, Cambridge, MA, 1963. 90 p.

- 2. D.J.C. MacKay and R.M. Neal. Near Shannon limit performance of low density parity check codes. Electron. Lett., Aug. 1996, vol.32, no.18. pp.1645-1646.

- 3. Р. Морелос-Сарагоса. Искусство помехоустойчивого кодирования. Методы, алгоритмы, применение. Перевод с английского В.Б. Афанасьева. М.: Техносфера, 2005. 319 с.

- 4. Z. Li, L. Chen, L. Zeng, S. Lin, and W.-H. Fong. Efficient Encoding of Quasi-Cyclic Low-Density Parity-Check Codes. IEEE Trans. Commun., Jan. 2005, vol. 54, no. 1. pp. 71–81.

- 5. IEEE P802.15.3c/July 2007, Wireless Personal Area Network (WPAN) Standard Physical Layer (PHY) specifications (Draft).

- 6. S. Lin and D.J. Costello Jr., Error Control Coding: Fundamentals and Applications, 2nd ed. Upper Saddle River, NJ: Prentice-Hall, 2004. 1260 p.

- 7. S. Lin, Qusi-Cyclic LDPC Code. CCSDS working group white paper, Oct. 2003.

- 8. D. Hocevar. A Reduced Complexity Decoder Architecture via Layered Decoding of LDPC Codes. In EEE Workshop on Signal Processing System, SISP 2004, pp. 107-112.

- 9. M. Mansour and N.R. Shanbhad. High-throughput LDPC decoders. IEEE Trans. VLSI Syst., Dec. 2003, vol. 11, no. 6. pp. 976-996.

- 10. T. Brack, M. Alles, T. Lehning-Enden, F. Kienle, N. Wehn, N.E. L'Insalata, F. Rossi, M. Rovini, L. Fanucci. Low Complexity LDPC Code Decoders for Next Generation Standards. Design, Automation & Test in Europe Conference & Exhibition, 2007. DATE '07.

- 11. Кравченко А.Н. Снижение сложности декодирования низкоплотностного кода. «Цифровая обработка сигналов». 2010, № 2, С.35-41.

- 12. Кравченко А.Н. Методы и аппаратура кодирования и декодирования систематического нерегулярного кода повторения накопления (IRA) для DVB-S2 и DVB-T2 демодуляторов. «Цифровая обработка сигналов». 2009, № 4, С.41-47.

# METHODS AND APPARATUS FOR ENCODING AND DECODING QUASI-CYCLIC LOW DENSITY PARITY-CHECK CODES

### Kravchenko A.N.

The analysis of the parity check matrices of irregular quasi-cyclic low-density codes (QC-LDPC) of WPAN (IEEE 802.15.3c) standard is performed. It is established that the parity check matrices are quadratic and invertible. In this connection, for the calculation of generator matrices can be used the traditional method with application to quasi-cyclic low-density codes.

The encoding and decoding methods are proposed based on the parity check matrices. The apparatus of a hardware encoding of these codes are suggested. Result of performance simulation of the decoder for QC-LDPC codes of WPAN standard over AWGN channel is presented.